Research on Vacuum Chamber of Chip-scale Atomic Beam Clocks

-

摘要:

近年来,一系列技术(包括激光冷却、光子集成和真空技术)的进步,使得原子束钟的微型化成为可能。芯片级原子束钟兼具现有微波原子束钟的高频率稳定性和CPT芯片原子钟的小体积、低功耗,具有很好的综合优势。国内有关芯片级原子束钟的报道很少。对芯片级原子束钟真空腔的关键制备技术进行系统研究,包括束源区、束漂移区以及微型准直通道阵列的微加工,以及多层微型真空腔结构的高气密封装。通过中间电极引出技术和阳极键合工艺的整体优化,减少并弱化了多层键合过程中反向电场对已形成键合面的损害,实现了高质量五层玻璃-硅键合结构。研究结果为实现高频率稳定度芯片级原子束钟,以及其他量子器件系统奠定了基本工艺基础。

Abstract:As two commonly used time-frequency reference devices today, the well-developed microwave atomic beam clocks have the disadvantages of large size and high-power consumption, while the chip-scale coherent population trapping (CPT) atomic clocks have poor long-term operational stability. In recent years, a series of technological advancements including laser cooling, photon integration, and vacuum technology have made it possible to miniaturize atomic beam clocks. Chip-scale atomic beam clocks are entirely fabricated by advanced MEMS technologies. They combine the high frequency stability of existing microwave atomic beam clocks with the small size and low power consumption of CPT chip atomic clocks, providing excellent comprehensive advantages. However, there have been few reports on chip-scale atomic beam clocks in China so far. Key preparation technologies of the vacuum chamber for chip-scale atomic beam clocks are systematically studied, including microfabrication of beam source cavity, beam drift cavity, and micro collimation channel array, as well as high airtightness packaging of multi-layer micro vacuum chamber structures. Based on optimized deep reactive ion etching technologies, common problems of undercutting and poor process controllability in wet chemical silicon corrosion process have been avoided, and high aspect ratio micro collimation channel arrays with steep sidewalls, smooth surfaces, and precise dimensions are obtained. Through the overall optimization of intermediate electrode extraction technology and anode bonding process, the damage of reverse electric field to the formed bonding interfaces during multi-layer bonding process has been reduced and weakened, and a high-quality five-layer bonding structure of glass and silicon is achieved. This study has laid the basic process foundation for realizing high-frequency stable chip-scale atomic beam clocks and other quantum device systems.

-

0. 引言

原子钟是最精确的时间和频率标准装置[1],在通信、勘测、雷达、基础研究等领域发挥着重大作用[2-3]。目前的原子钟应用系统都迫切需求小体积和低功耗,相应要求原子钟实现微型化、芯片化和集成化。

高精度光学原子钟受限于其工作原理,难以实现小型化[4]。传统的微波原子束钟,机械加工的微波腔体积难以减小[5]。基于MEMS技术的相干布居囚禁(CPT)芯片钟,是目前唯一实现商品化的芯片级原子钟[6]。但CPT原子钟的高气压环境会影响器件频率的长期稳定性,限制了其更广泛应用。

近年来激光冷却、光子集成及真空科技的进步,使得利用CPT芯片钟工艺实现微波原子束钟的微型化成为可能。2023年,美国国家标准与技术研究院等实现了首个芯片级原子束钟[7]。该器件工作原理和传统微波原子束钟相同,但制备完全基于MEMS工艺。通过将立体微波腔转换为玻璃-硅键合的二维平面漂移腔,并与之对应实现平面化的束源腔和准直通道,原子束钟的体积和质量均降低了2~3个数量级,实现了真正的微型化和低功耗。芯片级原子束钟既具备微波原子束钟频率稳定性高的固有优点,又具有CPT芯片原子钟的体积小、功耗低的特点,有很好的综合优势和应用前景。

然而迄今为止,国内芯片级原子束钟的相关报道和原型器件很少。本文拟对该器件特别是其真空腔的关键制备技术进行系统研究,采用深硅刻蚀技术实现准直通道微加工,采用定位边错位接触技术,以及边缘镀膜导电技术解决多层键合结构的中间电极引出问题,减少反向电场的解键合效应,实现高强度键合和高气密封装,为实现芯片级原子束钟,以及其他相关量子器件系统奠定基本工艺基础。

1. 问题分析

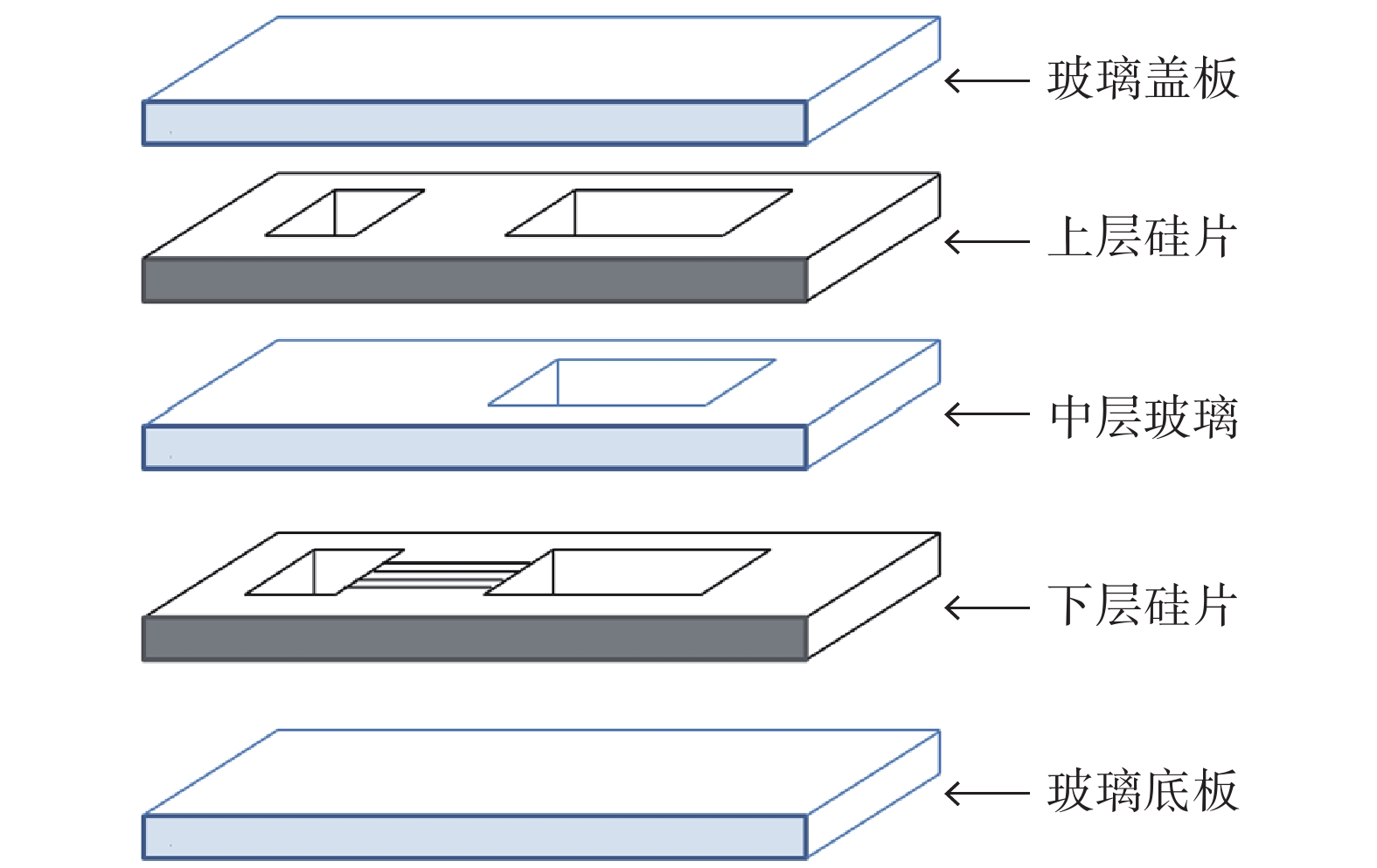

芯片级原子束钟真空腔的物理结构如图1所示,包括玻璃盖板、上层硅片、中层玻璃、下层硅片和玻璃底板,上层硅片包含束源区透光孔和漂移区孔,中层玻璃包含漂移区孔,下层硅片包含束源区孔、漂移区孔和准直通道。准确设计准直通道尺寸和各层厚度,保证通道相对漂移腔水平及垂直均居中。

玻璃图形通过激光切割或超声加工,硅片图形视具体结构及工艺要求采用化学腐蚀[8],或者深反应离子刻蚀[9](DRIE)方法。多层结构封装通过键合技术实现,可以从阳极键合、共晶键合、熔融键合、焊料键合和黏合剂键合等 [10-12]技术中优选。

阳极键合是玻璃与硅片封装的首选工艺,具有温度低、强度大、工艺简单的优点[13-14]。阳极键合适合构建真空,键合界面中空气及水分子被抽离,可以增加键合点的数量,获得更好的键合质量。阳极键合的MEMS谐振器,真空漏率达到3.85×10−9 Pa·m3/s[15],碱金属原子气室可实现10−11~10−13 Pa·m3/s[16-17]。

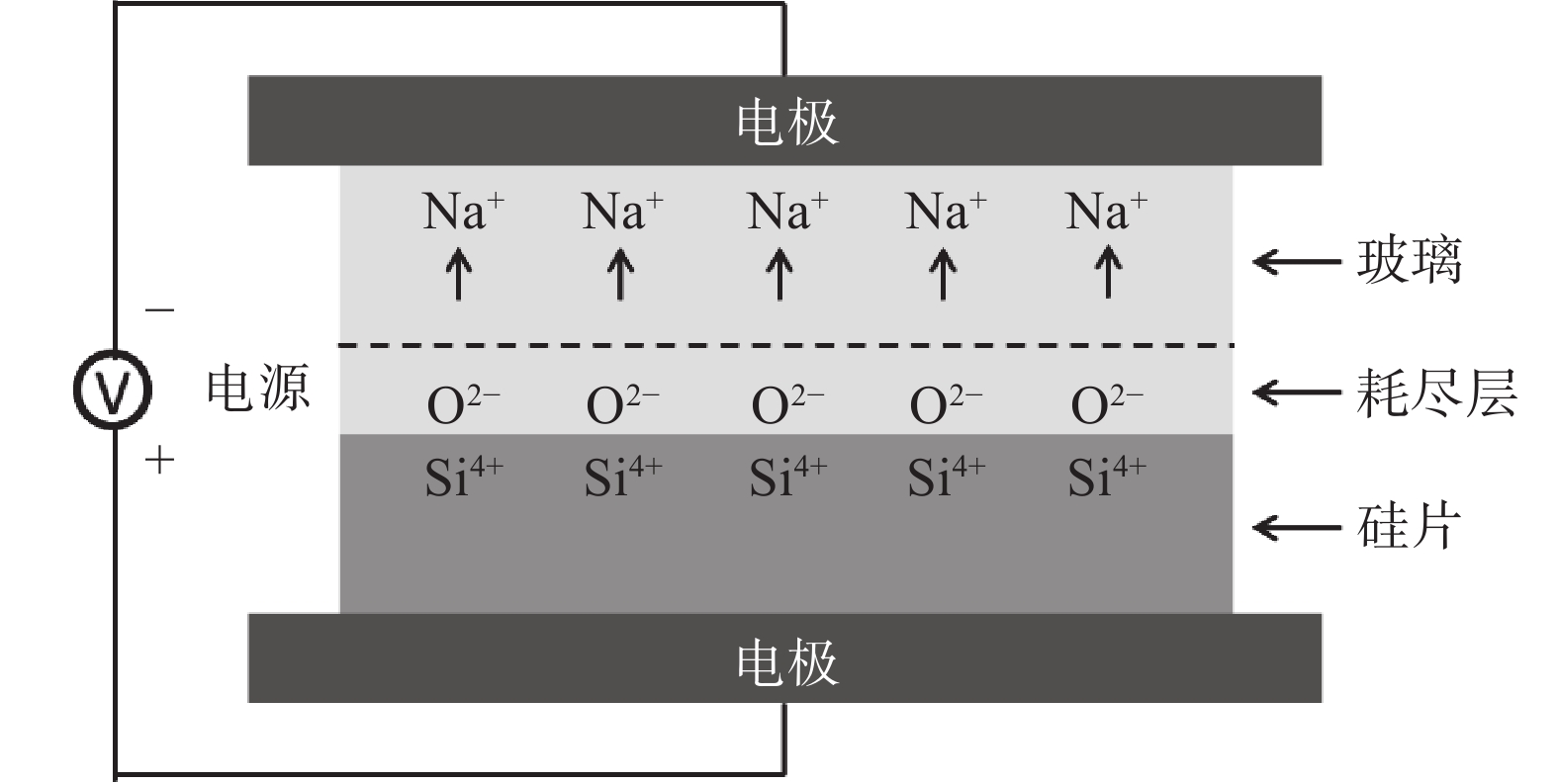

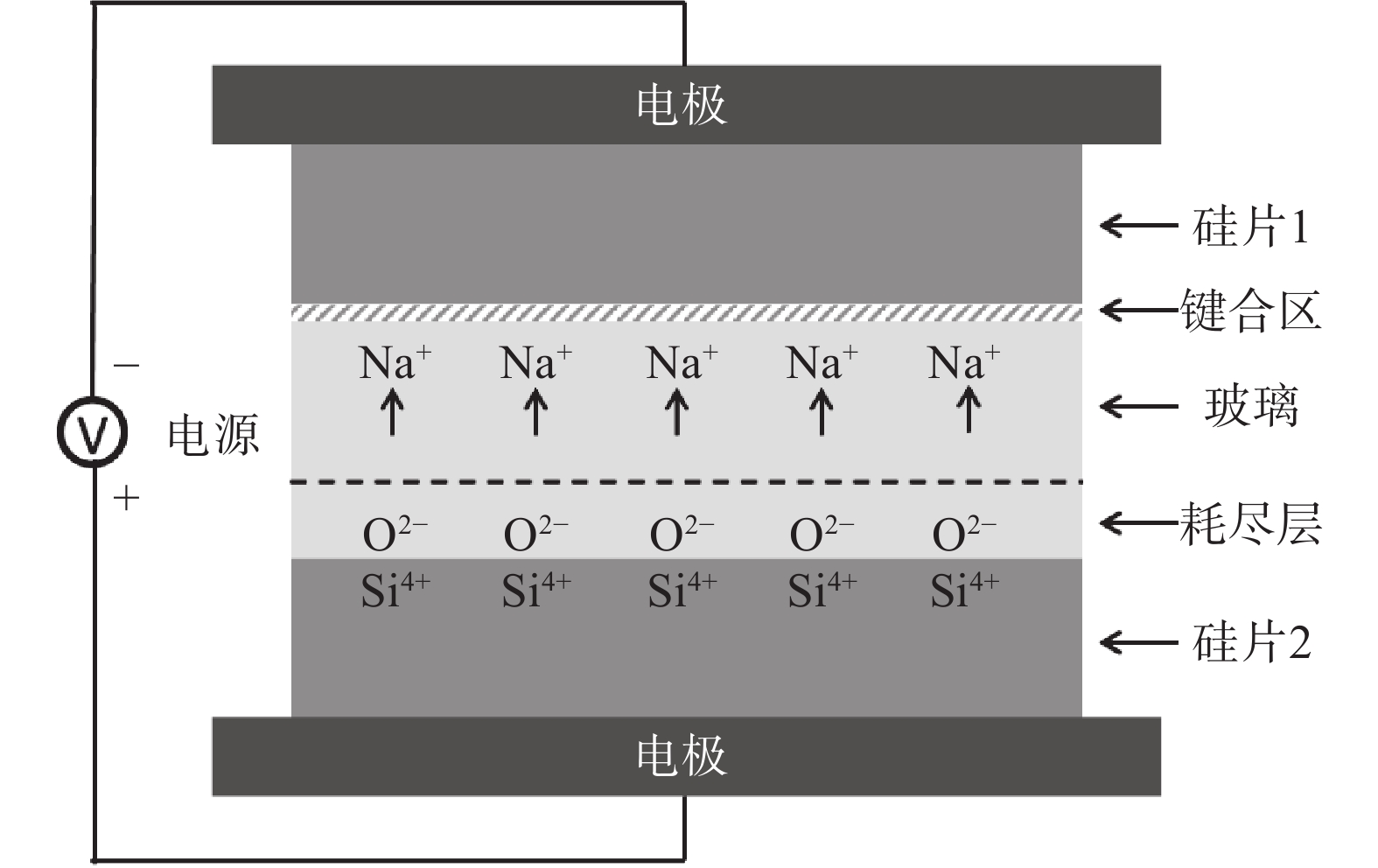

阳极键合原理如图2所示[18],对玻璃和硅片施加压力使之紧密贴合,保持几百度加温,对玻璃加负电压,硅片加正电压。玻璃中Na+受电场作用,向远离接触面的方向漂移,同时O2−在接触面附近积聚,形成带负电的耗尽层。耗尽层在接触面硅片中诱生镜像正电荷,产生强静电力,电场撤去后静电力不会全部消失。高温下,紧密接触的表面发生化学反应,会形成牢固的Si-O化学键。静电力和化学键共同作用,使硅片和玻璃结合一体。阳极键合开始后随着玻璃和硅片贴合面积增至最大,电流迅速增大达到峰值;而后随界面Si-O化合物增多及耗尽层增宽,电流逐渐减小并稳定在一个极小值。

真空腔构建至少需要三层结构,涉及两个键合界面。最简单的三层键合是通过一次电极反接转换,顺序进行两次键合[19]。然而研究发现,第二次键合时,反向电压会削弱一次键合面,降低键合质量。

对于玻璃-硅-玻璃结构,通过中间层引出共用阳极,可以避免键合面反向电压,直接实现三层键合[20]。中间层引出通常为点接触电极,相对面电极键合速度较慢、强度稍低,但能有效减少界面夹杂气泡 [21]。通过对中间硅片加工外凸结构,容易实现中间层的可靠引出,由此实现的微型真空三极管,键合面漏率可达10−11 Pa·m3/s[22]。

综上分析,实现多层结构微真空腔制备的关键,是减少反向解键合影响的同时,实现中间层的电极有效引出。

2. 方案设计与实施

2.1 方案设计

采用多叠层真空腔结构,中间玻璃片和硅片加工图形,封装后形成相应的束源区、漂移区和准直通道。具体工艺及检测流程如下。

玻璃通孔采用激光切割,硅片加工初期采用化学腐蚀,利于加速键合研究;工艺成熟后采用DRIE方法,利于得到高质量通道阵列和微空腔。

层间结合采用阳极键合,为减小反向电场影响,结合中间电极引出技术首先分别实现三层和两层结构,而后再将二者键合一体。

键合设备具备点接触电极时,中间电极引出可采用定位边错位接触技术。玻璃-硅片首次进行错位键合,再次键合时,通过点电极避过玻璃直接触碰中间硅片加电,避免电流流过已有键合面。本研究提出边缘镀膜导电技术,在已形成结构一侧表面及边缘制备导电膜,通过薄膜导电跨过玻璃连通中间硅片。边缘镀膜导电技术无须设备具有点接触电极,并能克服错位点接触技术只能键合有限层数的缺点,可用于实现更多层的复杂结构。

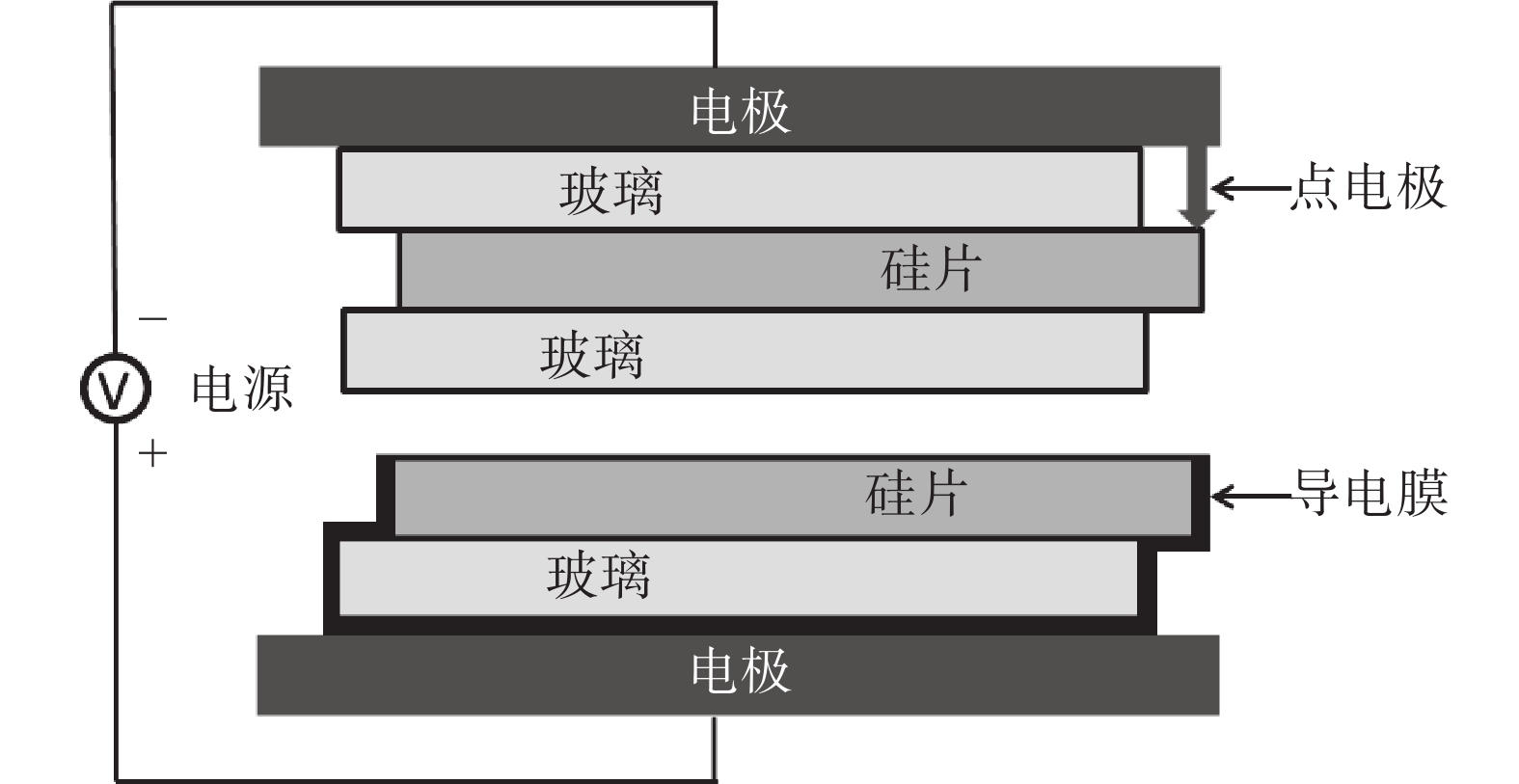

整体键合流程如图3所示。将通过定位边错位、两次键合形成的三层结构置于负电极,中间硅仍采用点电极引出;将已键合的两层结构蒸镀导电膜后,置于正电极;而后再次阳极键合,将两部分封装一体形成五层完整结构。

虽然最后一步键合,仍会在上层硅片和中间玻璃的键合面形成反向电场,但已无法避免,只能通过工艺优化减小影响。

多层真空腔的键合遵循渐进过程,依次采用无图形基片、简单图形基片摸索优化工艺,最后采用正式图形基片完成结构。

2.2 方案实施

玻璃片和硅片使用前进行标准RCA清洗,每步工艺结束,均进行丙酮与酒精超声、纯水冲洗、烘箱烘干,保证整个流程中表面洁净。

硅片化学腐蚀使用氢氧化钾(KOH)溶液,浓度控制在10%~30%,温度控制在60~90 ℃,发生如下反应:

$$ \mathrm{2KOH+Si+H}_{ \mathrm{2}} \mathrm{O=K}_{ \mathrm{2}} \mathrm{SiO}_{ \mathrm{3}} \mathrm{+2H}_{ \mathrm{2}} $$ (1) 硅片DRIE刻蚀采用标准Bosch工艺,发生如下反应:

$$ \mathrm{e+SF}_{ \mathrm{6}} \mathrm{=CF}_{ \mathrm{5}}^{ \mathrm+} \mathrm{+F}^{ \mathrm{*}} \mathrm{+2e} $$ (2) $$ \mathrm{F}^{ \mathrm{*}} \mathrm{+4Si=SiF}_{ \mathrm{4}} $$ (3) 阳极键合采用键合温度为300 ℃,电压为800 V,压力为50 kPa等基本参数。

导电层采用磁控溅射100 nm金属膜层,形成良好台阶覆盖,确保侧壁薄膜有效连通中间硅片。

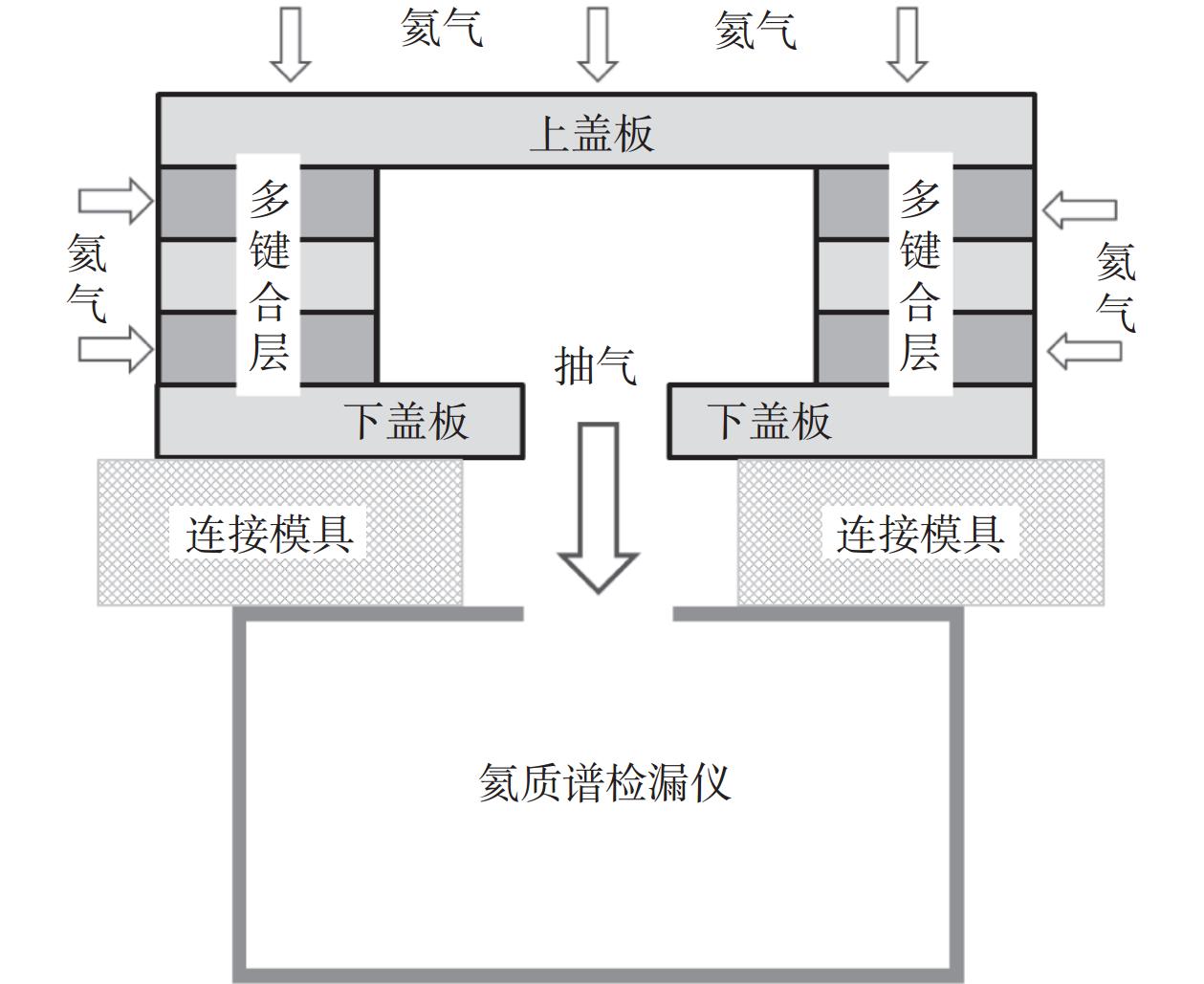

微型叠层真空腔的气密性检测,不考虑无损检测时,采用氦质谱检漏仪直接测量。如图4所示,将真空腔的一侧玻璃钻孔,通过设计专用模具与检漏仪真空系统相连,而后向真空腔各键合界面喷吹氦气,观测检漏仪测得漏率。

3. 结果及分析

3.1 无反向电场的键合

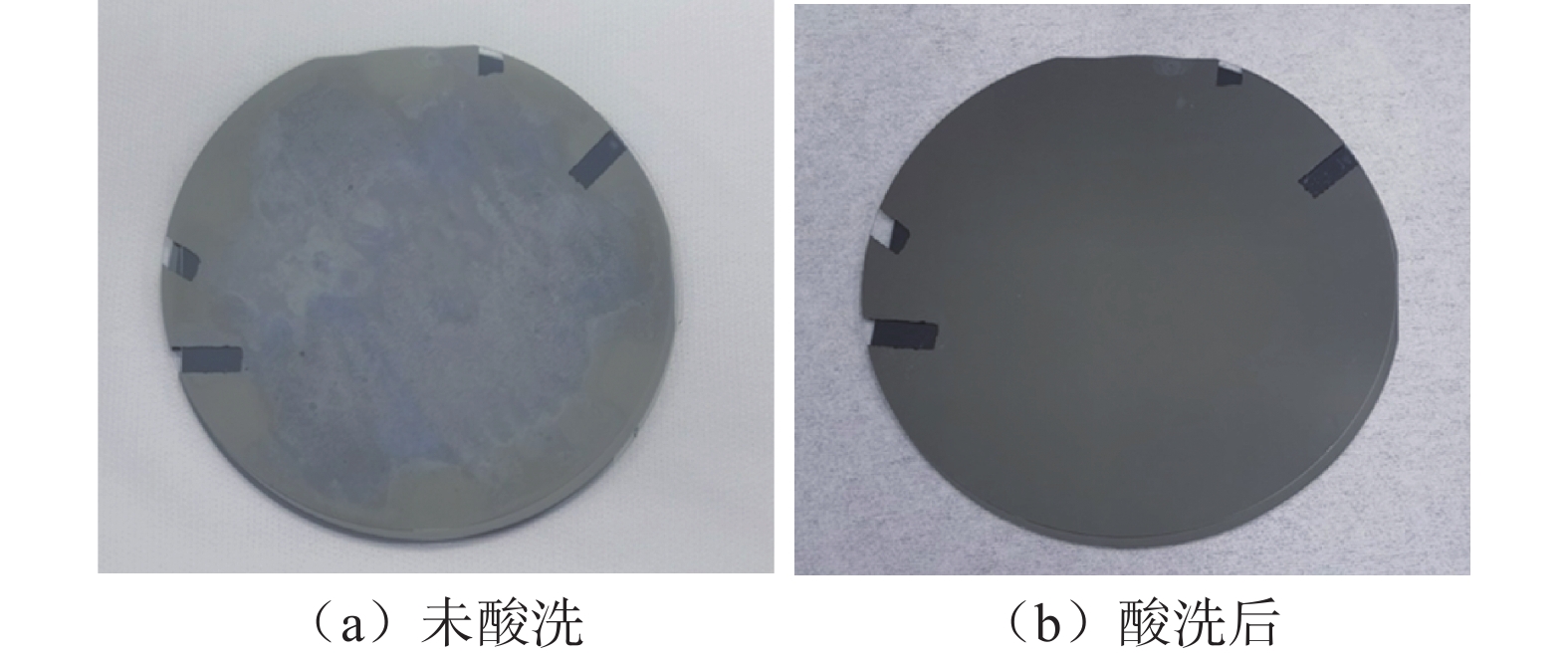

玻璃-硅以及玻璃-硅-玻璃多层键合,可以规避反向电场,工艺实现相对简单,值得注意的问题是玻璃表面的Na+析出。电场作用下定向迁移的Na+,在玻璃面析出后形成玷污,会影响后续键合,必须酸洗处理。这种表面玷污,在镀膜后尤为明显,图5对比结果表明了酸洗的必要性。

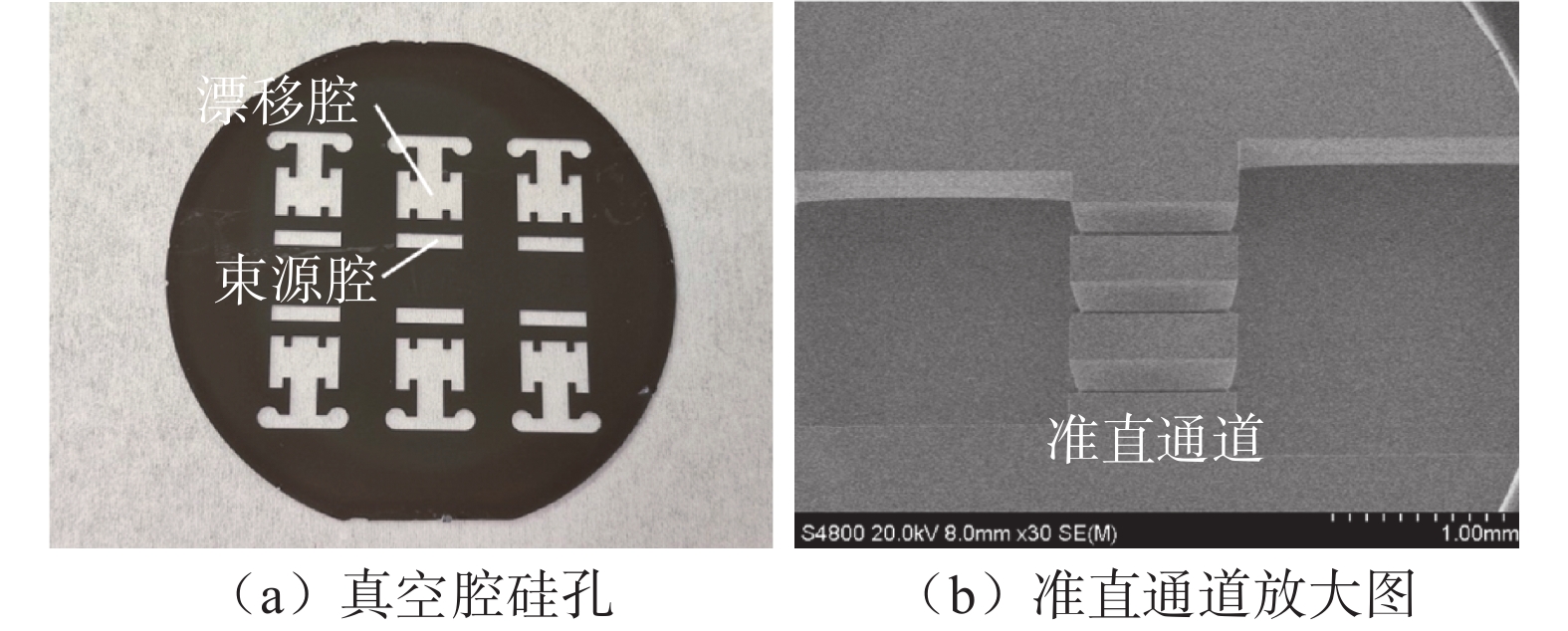

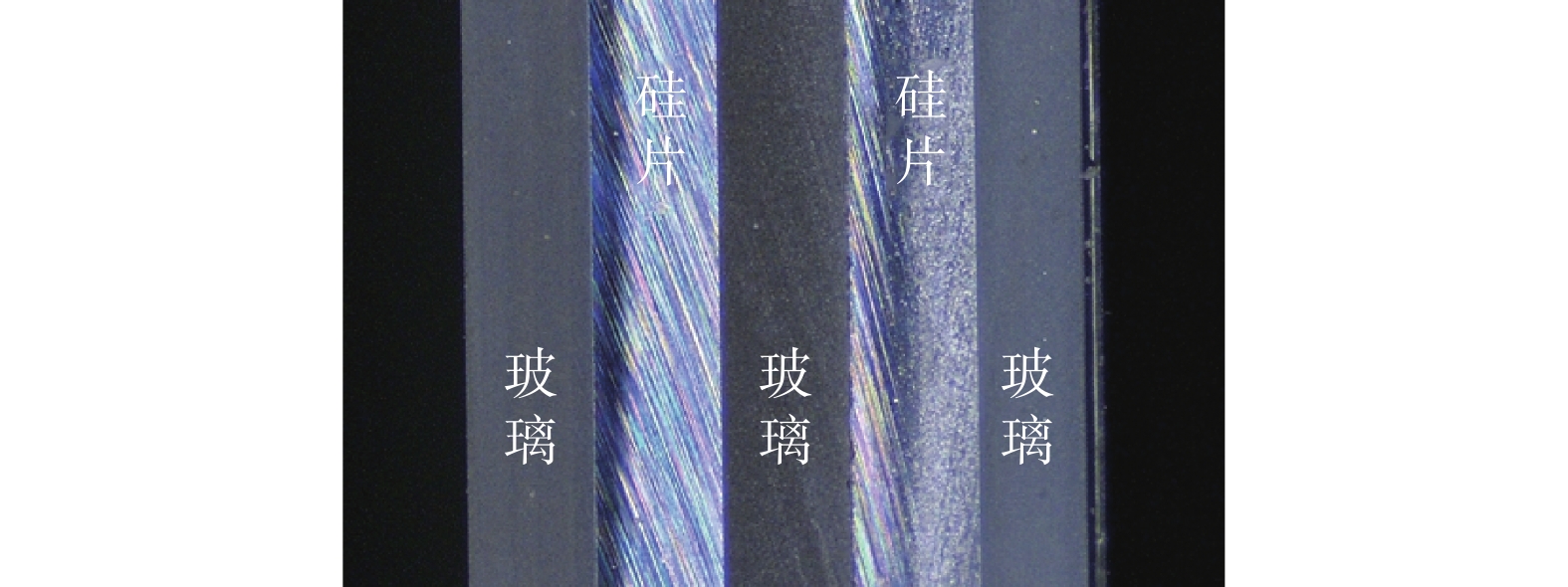

工艺试验片图形为毫米级方孔阵列,构成真空腔的图形包括束源腔孔、漂移腔孔以及连通二者的准直通道。正式硅片图形加工采用DRIE工艺,实现的图形表面光滑、边缘陡直,准直通道阵列规则一致,其光学与扫描电镜局部放大图如图6所示。

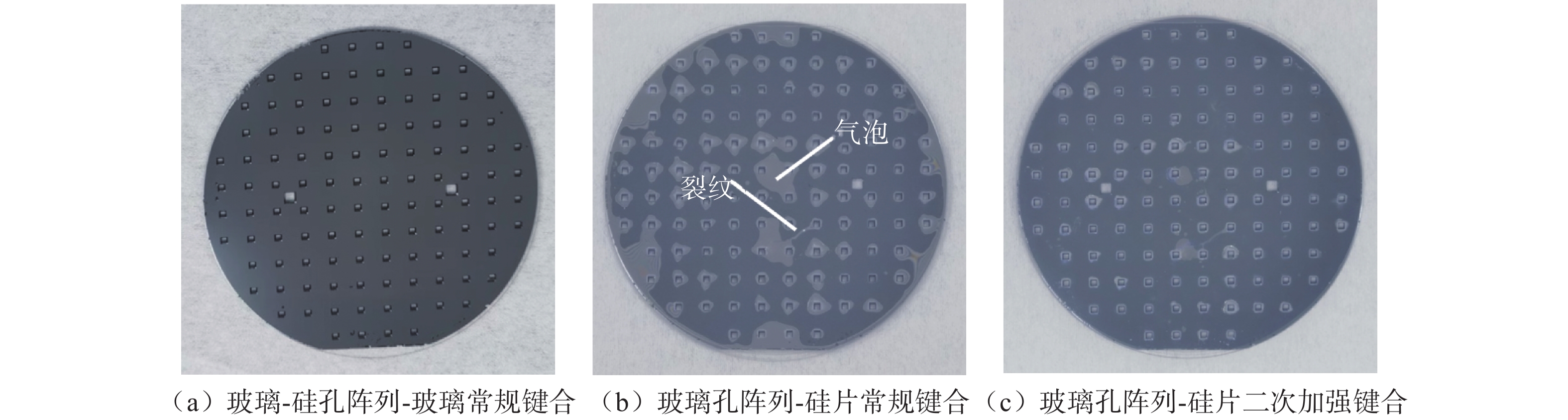

硅图形和玻璃的阳极键合相对容易,由玻璃-孔硅阵列-玻璃经两次键合形成的真空腔阵列,如图7(a)所示,键合牢靠,无明显气泡,键合强度约为10 MPa,漏气率可达10−13 Pa·m3/s量级。而玻璃图形和硅初步键合结果却不理想,如图7(b)所示,小孔附近和孔间均存在气泡,并出现轻微键合裂纹。即使再次经过400 ℃、

1000 V、50 kPa的增强键合,对气泡的改善效果有限。图7(c)为增强键合样品,虽然孔间气泡消失,但小孔边缘处气泡依然存在。分析认为出现气泡和裂纹的原因是玻璃表面的平整性被破坏。激光烧蚀玻璃孔的热效应,会在孔边缘导致凸起。表面轮廓仪检测表明,这种凸起高度可达微米量级,使得玻璃和硅片不能紧密贴合。解决方法是在不改变加工工艺前提下,采用非等尺寸设计,将玻璃孔适当缩减,使得键合时玻璃孔边缘凸起收缩在硅孔内部区域,避免和硅片平面直接碰触。

3.2 存在反向电场的键合

涉及反向电场的阳极键合较为复杂,反向电场会削弱已形成的键合面,甚至导致结构解键合。研究发现,使用统一参数键合得到的五层结构,在最终晶圆划切时部分芯片会分层脱开,表明键合面受到了破坏。

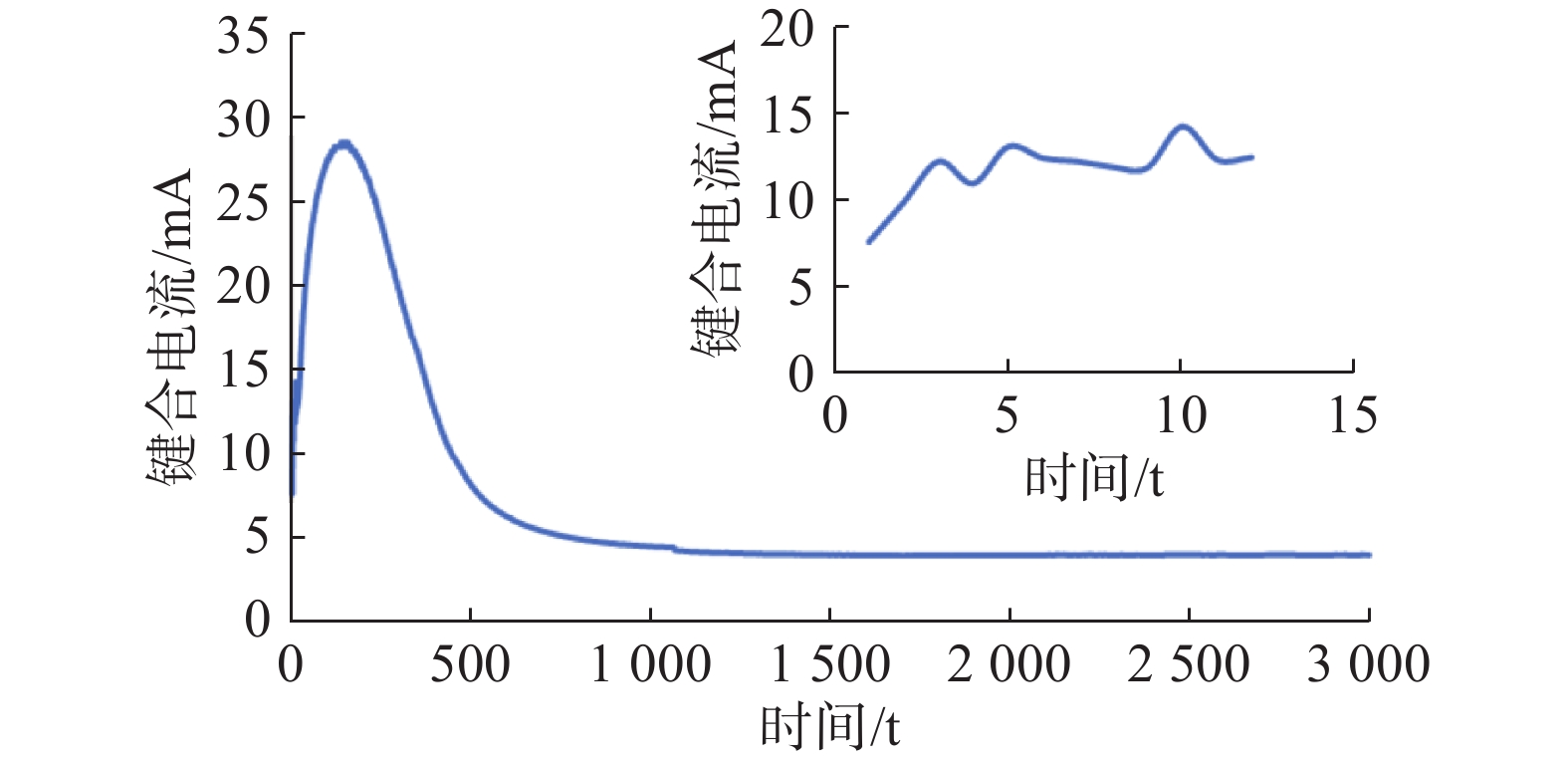

图3流程的最后一步键合可以由图8诠释,简化为硅片2和已形成的硅片1-玻璃一体结构之间的键合。此时硅片2和玻璃界面产生常规键合,电流变化是典型的尖峰缓降平稳曲线。而在硅片1和玻璃已键合区附近情况较为复杂,电场驱动的Na+向键合区行进过程中,会依次经过只存在 Na+空位的“低场强”区,以及存在Na+和 O2−空位的“高场强”区,由于“高场强”区空位数量巨大,Na+进入时迁移速率加快,宏观表现也为电流突增尖峰[23]。

硅-玻璃-硅结构的第二次键合,其典型电流变化是双界面叠加的双峰值缓降平稳曲线,主峰是二次键合面的键合峰,副峰源自一次键合面的离子快速迁移。调研及实验均表明,电流副峰是该过程的普遍现象,并且副峰电流变化并不规律,相同条件也会出现不同的电流突变特征。但一个普遍规律是,低温、低电压键合的电流突变会有所减弱。

反向电场对阳极键合面的损害有两个方面,表现为静电键合力削弱以及Na+析出集聚效应。反向电场的Na+迁移,会使先前形成耗尽层中的Na+浓度升高,尽管不能恢复到初始状态,但会诱导中和键合面附近的部分O2−,削弱静电键合力[24]。尽管没有证据表明Na+析出能直接破坏Si-O化学键,但研究中发现,Na+在界面键合缺陷处析出产生集聚,能形成析出斑和破坏区,降低键合强度。同样地,低温、低电压下缩短键合时间,有助于减弱Na+析出集聚效应[25]。

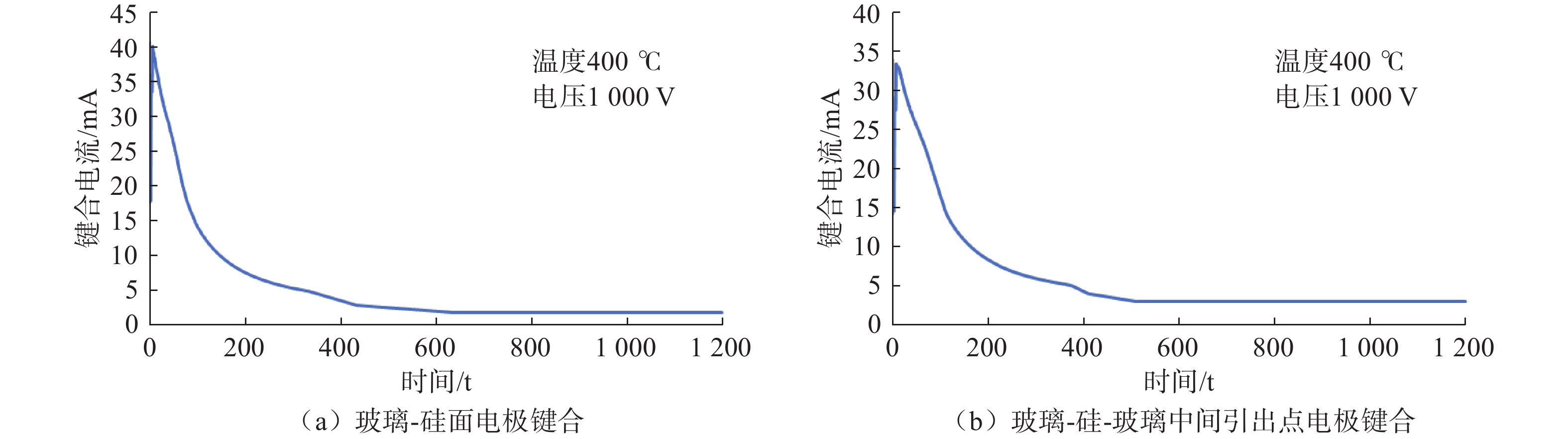

根据结果分析,提出多层键合优化的工艺流程。对玻璃-硅双层结构,以及玻璃-硅-玻璃三层结构采用强键合参数,键合温度为400 ℃、电压为

1000 V、压力为0.1 MPa,对应的键合电流-时间曲线对比如图9所示。玻璃-硅双层结构的面电极键合,加电后电流迅速达到约为40 mA的极大值,而后经过380 s缓慢下降至4 mA,1200 s键合结束时极小值约为2 mA。而玻璃-硅-玻璃三层结构的点电极键合,电流极大值约为33 mA,降至峰值电流的10% (3.3 mA)时间为480 s,1200 s时极小值约为3 mA。点电极键合相对电流较弱、时间较长,这与前述对比分析吻合。将这两种结构再次键合形成最终五层结构时,保持压力不变,温度降至300 ℃,电压降至800 V,确保新键合面强度,同时避免过度伤害已有键合面。对应该步骤的典型键合电流-时间曲线如图10所示,为更好显示电流主要变化趋势,仅保留了

3000 s的数据。结果发现,本过程和前述硅-玻璃-硅结构的第二次键合不尽相同。首先是曲线没有如文献[24]的明显双峰,仅在键合初期有小幅电流跃动,如插入图所示。产生该现象的原因目前尚不明晰,初步认为和点接触、边缘导电接触以及由此带来的界面变化相关。其次是该键合过程相对漫长,加电140 s后电流才达到28 mA的极大值,在1600 s时下降至4 mA,并在此后长达4 h的键合过程中基本不再变化。无反向电场结构采用强键合提高键合强度,有反向电场结构采用弱键合兼顾多层界面的组合方法,实现了玻璃-硅五层键合结构,划片后端面50倍显微照片如图11所示。尽管在4 h的键合过程中,电流并未下降至峰值电流的10% (2.8 mA)以下,该结构承受划片冲击后并无损伤,各键合面处硅片和玻璃均紧密接触无缝隙,表明了良好的键合结果。

4. 结论

针对芯片级原子束钟的真空腔结构,设计了工艺流程,并进行相应制备研究,为实现芯片级原子束钟奠定良好的工艺基础。

采用DRIE工艺,在硅基片制备了束源腔孔、漂移区孔、微型准直通道等芯片原子束钟的关键结构,表面光滑、边缘陡直,准直通道阵列规则一致,满足后续多层键合要求。激光烧蚀玻璃通孔简单方便,但其热效应导致的微米级边缘微凸会影响键合效应,需要通过结构设计优化避免。

不存在反向电场的结构键合相对容易,玻璃-硅孔-玻璃键合微空腔,可实现10 MPa量级的键合强度和10−13 Pa·m3/s量级的漏率。反向电场会影响已存在的键合面,削弱键合质量,甚至可能产生解键合。提出边缘薄膜导电创新技术,实现中间电极引出,减少反向电场解键合面的产生,提高键合质量。边缘薄膜导电技术避免了点电极引出方法对键合设备的特殊要求,以及对键合层数的限制,可扩展用于实现更多层复杂结构。基于反向电场削弱键合分析进行工艺优化,提出先强后缓的变参数键合组合模式,保障新键合面强度的同时不过度削弱已形成键合面,实现了高质量五层玻璃-硅键合结构。

基于上述结果,后续研究于聚焦微腔室封装及部件装填,包括碱金属源、吸气剂、吸收剂等,实现器件原型结构和基本功能。更进一步,开展芯片原子束钟结构优化设计,探索规避解键合效应的新结构和新工艺,以期提供更稳定的高真空环境,实现更好的器件频率稳定性。

-

-

[1] 王义遒. 原子钟及其进展[J]. 物理教学,2003,25(4):2−4. [2] KNAPPE S,SCHWINDT P,SHAH V,et al. A chip-scale atomic clock based on 87Rb with improved frequency stability[J]. Optics Express,2005,13(4):1249−1253. doi: 10.1364/OPEX.13.001249

[3] EKLUND E J,SHKEL A M,KNAPPE S,et al. Glass-blown spherical microcells for chip-scale atomic devices[J]. Sensors & Actuators a Physical,2008,143(1):175−180.

[4] BLOOM B J,NICHOLSON T L,WILLIAMS J R,et al. An optical lattice clock with accuracy and stability at the 10−18 level[J]. Nature,2013,7488(506):71−75.

[5] 杨巧会,潘多,陈景标. 芯片级原子钟研究进展[J]. 真空电子技术,2023(1):1−11. [6] KNAPPE S,SHAH V,SCHWINDT P D D,et al. A microfabricated atomic clock[J]. Applied Physics Letters,2004,85(9):1460−1462. doi: 10.1063/1.1787942

[7] MARTINEZ G D,LI C,STARON A,et al. A chip-scale atomic beam clock[J]. Nature Communications,2023(14):3501.

[8] ELWENSPOEK M,JANSEN H. 硅微机械加工技术[M]. 北京:化学工业出版社,2007:1−348. [9] WU B,KUMAR A,PAMARTHY,S. High aspect ratio silicon etch:A review[J]. Journal of Applied Physics,2010,108:051101. doi: 10.1063/1.3474652

[10] HILTON A,TEMPLE D S. Wafer level vacuum packaging of smart sensors[J]. Sensors,2016(16):1819−1851.

[11] WANG H Y,FOOTE R S,JACOBSON S C,et al. Low temperature bonding for microfabrication of chemical analysis devices[J]. Sensors and Actuators:Chemical,1997,45(3):199−207. doi: 10.1016/S0925-4005(97)00294-3

[12] TANAKA S J. Wafer level hermetic MEMS packaging by anodic bonding and its reliability issues[J]. Microelectronics Reliability,2014(54):875−881.

[13] LUO Z Y,CHEN D Y,WANG J B,et al. A high Q resonant pressure microsensor with through glass electrical interconnections based on wafer level MEMS vacuum packaging[J]. Sensors,2014(14):24244−24257.

[14] WEICHEL S,REUS R D,BOUAIDAT S,et al. Low-temperature anodic bonding to silicon nitride[J]. Sensors & Actuators A Physical,2000,82(1/3):249−253.

[15] 郑雅欣,阮勇,祝连庆,等. 圆片级封装中的二次硅-玻璃键合工艺研究[J]. 传感器与微系统,2024,43(10):50−54. [16] SU J,DENG K,GUO D Z,et al. Stable 85Rb micro vapor cells:fabrication based on anodic bonding and application in chip-scale atomic clocks[J]. Chinese Physics B,2010,19(11):110701. doi: 10.1088/1674-1056/19/11/110701

[17] 杜婷,李兴辉,韩攀阳,等. 高气密性碱金属微气室低温阳极键合技术研究[J]. 传感器与微系统,2020,39(11):14−17. [18] WALLIS G,POMERANTZ I. Filed assisted glass-metal sealing[J]. Journal of Applied Physic,1969,40(10):3946−3949. doi: 10.1063/1.1657121

[19] 张廷凯,甘志银,张鸿海. 两电极多层阳极键合实验研究[J]. 传感器与微系统,2009,28(7):21−23. doi: 10.3969/j.issn.1000-9787.2009.07.007 [20] 秦会峰,孟庆森,胡立芳. 玻璃/铝多层结构间阳极键合机理及界面微观分析[J]. 兵器材料科学与工程,2014,37(6):39−42. doi: 10.3969/j.issn.1004-244X.2014.06.011 [21] JOYCE R,SINGH K,VARGHESE S,et al. Stress reduction in silicon/oxidized silicon–Pyrex glass anodic bonding for MEMS device packaging:RF switches and pressure sensors[J]. Journal of Materials Science:Materials in Electronics,2015,26(1):411−423. doi: 10.1007/s10854-014-2415-z

[22] 陶俊明,刘文超,郭等柱,等. 片上电子源的真空阳极键合[J]. 真空电子技术,2024(4):28−33. [23] ALBAUGH K B,RASMUSSEN D H. Rate processes during anodic bonding[J]. Journal of the American Ceramic Society,1992,75(75):2644−2648.

[24] 陈大明,胡利方,时方荣,等. 硅-玻璃-硅阳极键合机理及力学性能[J]. 焊接学报,2019,40(2):123−127. [25] VISSER M M,PLAZA J A,WANG D T,et al. Chemical analysis of bonded and debonded silicon-glass interfaces[J]. Journal of Micromechanics and Microengineering,2001,11(5):1−6. doi: 10.1088/0960-1317/11/5/401

下载:

下载: